During my time at NUS, I took modules under the Electrical and Computer Engineering (ECE) department to map to pillar modules at SUTD. I found that the curriculum at NUS was a lot more content-focused, especially for higher-level modules. Apart from pillar modules, NUS also offers a wide range of courses that can be mapped to HASS subjects at SUTD. As such, I took the opportunity to take up a language module (French), since it was not something that SUTD offers.

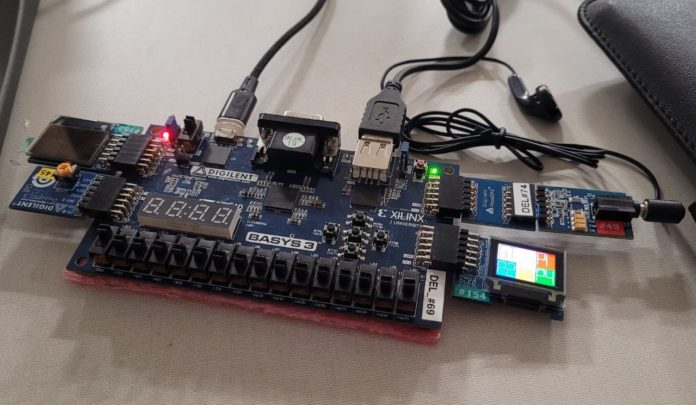

The module I found most fulfilling (despite the heavy workload) was EE2026. A simple search of the module on NUSMods did scare me quite a bit, but I took it since it was a restricted module for my EPD track. However, the fact that it is a grade-free semester for me did relieve some stress, hence I could enjoy the learning process a bit better. The curriculum is very well-structured, and the professors are clear and thorough with their explanations. The three fundamental lab sessions were done before recess week, and are meant to introduce us to Verilog which would be heavily used in the project in the second half of the term. They slowly build up in difficulty, and the learning objectives were clear and well-explained. The labs were quite fast-paced and the time given to finish the first 2 labs was about half a week, and about 1.5 weeks for the 3rd lab. The project was done in the second half of the semester. Before the project brief was released, I was afraid of not being able to find groupmates. Thankfully, I was approached by a group which needed 1 more member. The project was challenging, however, the process and outcome was very fulfilling. I am also thankful to have the opportunity to work with and learn from other NUS students during the project.